module demo1(

input B, D, // Declare inputs

output A, C // Declare outputs

);

// Content of module

assign C = ~A;

assign A = ~B & D;

endmoduleDeeper Dive on Verilog Syntax

Basics of Verilog Operations

| Operation | Verilog Syntax |

|---|---|

Single NOT | Y = ~A |

Bitwise OR | Y = A | B |

Bitwise AND | Y = A & B |

Bitwise XOR | Y = A ^ B |

Bitwise NOR | Y = ~(A | B) |

Bitwise NAND | Y = ~(A & B) |

Bitwise XNOR | Y = ~(A ^ B) |

Basics of Verilog Modules

The Top File

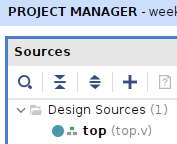

module top(

input [1:0] sw,

output [1:0] led

);

// This is an instantiation, not a function call

// Think of it like plugging in a circuit to a breadboard

demo1 uut(

.B(sw[0]),

.D(sw[1]),

.A(led[0]),

.C(led[1])

);

endmoduleVivado Tips on Top

Make sure that the top file is bolded and marked with the three blocks

Ensure to read the "How To Verilog"

Included in this lab is a document on how to read verilog

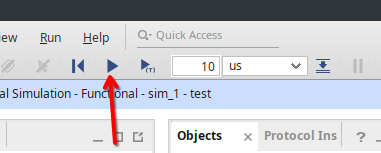

Frequently run Simulation

Ensure to hit "Run All" to finish sim