module byte_memory_ff(

input [7:0] data,

input store,

output reg [7:0] memory

);

always @(posedge store)

memory <= data;

endmoduleMaking Computers Count

Level vs Edge Sensitive

Level Sensitive

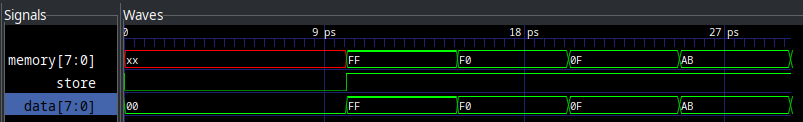

Figure 1. D-Latch Output

Edge Sensitive

Figure 2. Edge vs. Level Sensitivity

Edge detector and D-FlipFlop

Figure 3. Pulse Detector and D-Latch

Behavioral Implementation

State Tables

Excitation, Characteristic, and Truth Tables

Truth Table

Input | Qcurrent | Qnext |

0 | 0 | 0 |

0 | 1 | 0 |

1 | 0 | 1 |

1 | 1 | 1 |

Characteristic Table

Input | Qcurrent | Qnext |

0 | X | 0 |

1 | X | 1 |

Excitation Table

Qcurrent | Qnext | Input |

0 | 0 | 0 |

1 | 0 | 0 |

0 | 1 | 1 |

1 | 1 | 1 |